Operating System Learning Notes (7) Overview of I/O Management

I/O devices

I/O Facility Management is the most messy and challenging part of operating system design. Because it includes different devices and device-related applications in many fields, it is difficult to have a universal and consistent design solution. So before understanding Facility Management, you should first understand the specific types of I/O devices.

I/O devices in computer systems can be divided into the following types according to their usage characteristics:

- human-machine interaction External devices. Devices used to interact with computer users, such as printers, monitors, mice, keyboards, etc. The data exchange speed of such devices is relatively slow, usually in bytes.

- Storage devices. Devices used to store programs and data, such as disks, tapes, optical disks, etc. This type of device is used for data exchange, which is fast and usually uses blocks composed of multiple bytes for data exchange.

- Network communication equipment. Equipment used for remote device communication, such as various network interfaces, modems, etc. Its speed is between the first two types of devices. Network communication equipment is also very different from the first two types of devices in use and management.

Divided by transmission rate:

- Low-speed devices. A class of devices with a transmission rate of only a few bytes to hundreds of bytes per second, such as a keyboard, mouse, etc.

- Medium-speed equipment. A class of equipment with a transmission rate of thousands of bytes to tens of thousands of bytes per second, such as line printers, laser printers, etc.

- High-speed equipment. A class of equipment with a transmission rate of hundreds of kilobytes to gigabytes, such as tape drives, disk drives, optical drives, etc.

According to the information exchange unit, it is divided into:

- Block device. Since the access to information is always in units of data blocks, the device that stores information is called a block device, which belongs to structured devices, such as disks. The basic characteristics of disk devices are high transmission rates and addressable, that is, any block can be read and written randomly.

- Character equipment. The device used for data input and output is a character device, because the basic unit of transmission is a character. It belongs to the unstructured type, such as interactive end point machines, printers, etc., which is characterized by low transmission rate, unaddressable, and interrupt driving mode is often used in input and output.

I/O control mode

One of the main tasks of Facility Management is to control the transfer of data between devices and memory or processors.

There are 4 types of input and output between peripheral devices and memory.

The way the program is directly controlled

The computer reads data from external devices into memory, one word at a time. For each word read, the CPU needs to cycle through the peripheral state until it is determined that the word is already in the register of the I/O controller.

Due to the high speed of the CPU and the low speed of the I/O device, the CPU is in the cycle test of waiting for the I/O device to complete the data I/O most of the time, resulting in a great waste of CPU resources.

In this way, the reason why the CPU needs to constantly test whether it is completed is that the CPU does not use an interrupt mechanism, so that the I/O device cannot report to the CPU that it has completed the input of a word.

This method is simple to implement, but the disadvantage is that the CPU and I/O devices can only be serial.

Interrupt driven mode

Allows I/O devices to actively interrupt the CPU and request services, thereby freeing the CPU to continue doing other useful work after sending read commands to the I/O controller.

We can look at the working process of interrupt-driven mode from the perspective of I/O controller and CPU respectively.

From an I/O controller perspective:

- The I/O controller received a read command from the CPU

- Read data from the peripheral to the controller’s registers

- Send an interrupt signal to the CPU through the control line, indicating that the data is ready, and then wait for the CPU to request the data.

- After the controller receives the signal from the CPU requesting data, it puts the data on the data bus and transmits it to the registers of the CPU.

From a CPU perspective:

- The CPU issues a read command, then saves the context of the currently running program (such as program counters and processor registers, etc.), and then proceeds to execute other programs.

At the end of each instruction cycle, the CPU checks for interrupts. - If there is an interrupt from the I/O controller, the CPU saves the context of the current program and goes to execute the interrupt handler to process the interrupt. At this time, the CPU reads the data of this word from the I/O controller to the register and stores it in main memory.

- The CPU restores the program context that issued the I/O command and then continues execution.

What is an instruction cycle? [[Analysis] Instruction cycle, CPU cycle and clock cycle in CPU] (https://zhuanlan.zhihu.com/p/90829922)

Can I/O interrupts interrupt the time slice? [Normally, the thread can only use up the time slice to give up the cpu execution right?

Restore the original program context by reading a word?

DMA mode

The interrupt-driven mode is more effective than the direct program control mode, but since each word in the data is transmitted between the memory and the I/O controller through the CPU, the interrupt-driven mode still consumes a lot of CPU.

The basic idea of DMA (Direct Memory Access) is to open a direct data exchange channel between I/O devices and memory.

DMA mode features are as follows:

The basic unit is a data block.

- The data transferred is directly into memory from the device, or vice versa.

- CPU intervention is only required at the beginning and end of the transmission of one or more data blocks. The transfer of the entire block of data is done under the control of the DMA controller.

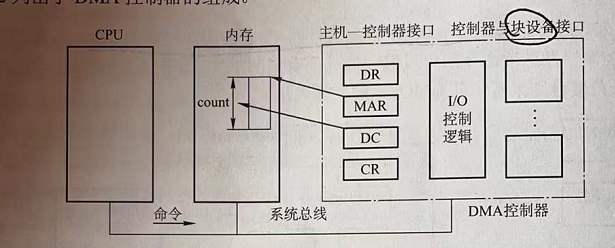

To achieve direct exchange of block data between the host and the controller, the following four types of registers need to be set in the DMA controller:

- Command/Status Register (CR). Used to receive I/O commands or related control information from the CPU, or device status words.

- Memory Address Register (MAR). On input, it stores the starting destination address for transferring data from the device to memory, and on output, it stores the memory source address from internal to the device.

- Data Register (DR). Used to temporarily store data from device to memory or from memory to device

- Data counter (DC). Stores the number of bytes (sections) to be transmitted this time.

As shown in the figure above, the working mode of DMA is: after the CPU receives the DMA request from the I/O device, it sends a command to the I/O controller, starts the DMA controller, and then continues other work. After that, the CPU delegates the control operation to the DMA controller, which is responsible for processing. The DMA controller interacts directly with the memory, transmitting the entire data block, one word at a time, and the entire process does not require CPU participation. After the transfer is completed, the DMA sends an interrupt signal to the CPU.

The main difference between the DMA control mode and the interrupt driving mode is that the interrupt driving mode interrupts the CPU when each data needs to be transmitted, while the DMA control mode interrupts the CPU only when the required batch of data is all transmitted.

Channel control mode

The I/O channel refers to a processor that is specifically responsible for input and output (note that this is not a controller). The I/O channel method is the development of the DMA method, which can further reduce the interference of the CPU, that is, the intervention of reading and writing a data block is reduced to the intervention of reading and writing a group of data blocks and related control and management.

At the same time, the parallel operation of CPU, channel and I/O devices can be realized, which can effectively improve the resource utilization rate of the entire system.

For example, when the CPU wants to complete a set of related read or write operations and related controls, it only needs to send one I/O instruction to the I/O channel to give the first address of the channel program to be executed and the I to be accessed./O device, after the channel receives the instruction, the channel program can be executed to complete the specified I/O task, and an interrupt request is sent to the CPU at the end of the data transfer.

The difference between I/O channels and general processors is:

- Single type of channel instruction.

Without its own memory, the channel program executed by the channel is placed in the memory of the host, that is, the channel shares memory with the CPU

Difference between DMA control mode and interrupt control mode

- The interrupt control mode interrupts the CPU after each data transfer is completed, while the DMA control mode interrupts the CPU after all the required data transfer is completed.

- The data transfer in the interrupt control mode is controlled by the CPU during interrupt processing, while the DMA control mode is completed under the control of the DMA controller. However, in the DMA control mode, the direction of data transfer, the memory address where the data is stored and the length of the transmitted data are still controlled by the CPU.

- The DMA mode takes the memory as the core, and the interrupt control mode takes the CPU as the core, so the DMA mode can work in parallel with the CPU.

- The DMA mode can transmit data in batches, and the interrupt control mode can only be in bytes.

Difference between DMA control mode and channel control mode

In the DMA control mode, data exchange can be performed in batches without CPU intervention between the device and the main memory under the control of the DMA controller, which not only reduces the burden on the CPU, but also improves the transmission speed of the I/O data.

The channel control mode is similar to the DMA control mode, and it is also a control mode that directly exchanges data between the device and the memory based on the memory. However, in the channel control mode, the CPU only needs to issue a start instruction to indicate the corresponding operation and I/O device of the channel., this instruction can start the channel and make the channel call out the corresponding channel execution program from the memory.

Compared with the DMA method, the channel control method requires less CPU intervention, and one channel can control multiple devices at the same time, further reducing the burden on the CPU.

In addition, for the channel, you can use some instructions to flexibly change the channel program, which DMA control can not do.

Hierarchy of I/O subsystems

| User layer I/O software |

|---|

| Device Independent Software |

| Device Drivers |

| Interrupt handler. |

| hardware |

The entire I/O system can be regarded as a system structure with 4 levels, each level and its function are as follows:

User layer I/O software

Implement the interface to interact with the user. The user can directly call the library functions related to I/O operations provided at the user layer to operate the device. Generally speaking, most of the I/O software is inside the operating system, but there is still a small part at the user layer, including library functions linked with user programs, and some programs that run completely outside the kernel. User layer software must obtain operating system services through a set of system calls.

Device independent software

It is used to realize the unified interface between user program and device driver, device command, device protection, device allocation and release, etc., and provide necessary storage space for Facility Management and data transmission.

Device independence also becomes device independence, making the application independent of the specific use of physical devices, in order to achieve device independence and the introduction of logical devices and physical devices two concepts.

In an application, a certain type of device is requested based on the logical device name; in actual execution of the system, the logical device name must be mapped to the physical device name for use.

The benefits of using logical device names are:

Increase the flexibility of equipment allocation.

Retargeting of I/O devices is easy.

In order to achieve device independence, another layer of device independence software must be set on top of the driver. Overall, the main functions of device independence software can be divided into two aspects:

- Perform common operations for all devices. Including: allocating and recycling devices; mapping logical devices to physical device names; protecting devices from direct user access to devices; buffer management; error control; providing unified logical blocks independent of devices, shielding between devices Differences in information exchange unit size and transmission rate.

- Provide a unified interface to the user layer (file layer). Regardless of the device, the interface they provide to the user should be the same, for example, read and write operations on various devices, read/write commands are used uniformly in the application program, etc.

Device driver

Directly related to hardware, responsible for the specific implementation of the operating instructions issued by the system to the device, driving the driver of the I/O device.

Usually, each type of device provides a device driver, which is a communication program between the I/O process and the device controller, often in the form of a process. The device driver provides a set of standard interfaces to the upper-level user program. The specific differences of the device are encapsulated by the device driver, which is used to receive abstract I/O requests from the upper-level software, such as read or write commands, which are converted into specific requirements and sent to the device controller. It also transmits the signals sent by the device controller to the upper-level software, thereby hiding the differences between device controllers for the I/O kernel subsystem.

Interrupt handler

The CPU environment used to save the interrupted process is transferred to the corresponding interrupt handler for processing. After processing and resuming the site of the interrupted process, the interrupted process is returned.

The main tasks of the interrupt processing layer are: switching the process context, testing the processing end point signal source, reading the device state and modifying the process state.

Since interrupt handling is closely related to hardware, it should be shielded as much as possible for users, so it should be placed at the bottom of the operating system, and other parts of the system should have as little relationship with it as possible.

Hardware equipment

I/O devices usually contain a mechanical component and an electronic component. In order to achieve the modularity and versatility of the design, they are generally separated:

- The electronic component is called a device controller (or adapter), and in a personal computer, it is usually a printed circuit board inserted into the main board expansion slot.

The mechanical part is the equipment itself.

A few points to note:

The device controller mentioned here refers to the controller inside the hardware device, not the controller in the previous DMA controller.

Device independence is the public operation of the device, such as permission authentication, error checking, and using caching to unify blocks of different sizes from different devices into blocks of the same logical size.

Specific system command parsing and execution require underlying device drivers.

Interrupt handlers are at the level of the entire operating system, not just used in I/O.

The device controller communicates with the CPU through registers. On some computers, these registers occupy a portion of the memory address, called memory image I/O; other computers use I/O-specific addresses, and the registers are addressed independently.

The operating system performs I/O functions by writing command words to the controller register. After the controller receives a command, the CPU can switch to other tasks and let the device controller complete the specific I/O operations on its own.

When the command is executed, the controller sends an interrupt signal, the operating system to re-obtain the execution authority of the CPU and check the execution result, then the CPU still reads information from the controller register to obtain the execution result and the status information of the device.

The main functions of the device controller are as follows:

- Receive and recognize commands sent by the CPU or channel, such as the disk controller can accept read, write, and find commands.

- Implement data exchange, including data transmission between devices and controllers, through data buses or channels, between controllers and main memory.

- Discover and record the status information of the device and itself for CPU processing.

- Device address recognition.

In order to achieve the above functions, the device controller must contain the following parts:

- Device controller and CPU interface. This interface has three types of signal lines: data lines, address lines and control lines. Data lines are usually connected to two types of registers, data registers (which store input data sent from the device or output data sent from the CPU) and control/status registers (which store control information sent from the CPU or device status information)

- Device controller and device interface. The device controller needs a corresponding number of interfaces to connect the device. One interface connects a device. There are three types of signals: data, control and status in each interface.

- I/O control logic. It is used to realize the control of the device. It interacts with the CPU through a set of control lines and decodes the I/O commands received from the CPU. When the CPU starts the device, it sends the start command to the controller, and at the same time sends the address to the controller through the address line. The I/O logic of the controller decodes the address and selects the device accordingly for control.